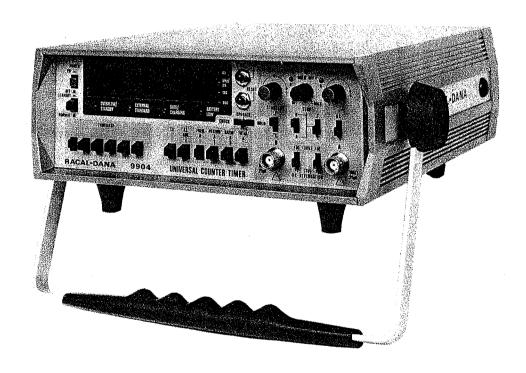

# Universal Counter-Timer 9904

Maintenance Manual

# **Racal-Dana Instruments Limited**

Duke Street, Windsor, Berks, England

Prepared by Group Technical Handbooks Department, Racal Group Services Limited

Ref. WOH 8155

Printed in England

Issue 3.2.82 -100

# **HANDBOOK AMENDMENTS**

Amendments to this handbook (if any), which are on coloured paper for ease of identification, will be found at the rear of the book. The action called for by the amendments should be carried out by hand as soon as possible.

#### 'POZIDRIV' SCREWDRIVERS

Metric thread cross-headscrews fitted to Racal equipment are of the 'Pozidriv' type. Phillips type and 'Pozidriv' type screwdrivers are <u>not</u> interchangeable, and the use of the wrong screwdriver will cause damage. POZIDRIV is a registered trade mark of G.K.N. Screws and Fasteners Limited. The 'Pozidriv' screwdrivers are manufactured by Stanley Tools Limited.

# CONTENTS

|           |                                                                                                                                                                                                                                                                   | Page                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|           | FRONTISPIECE                                                                                                                                                                                                                                                      |                                                                                    |

| SECTION 1 | TECHNICAL SPECIFICATION AND SUPPLEMENTARY DATA                                                                                                                                                                                                                    |                                                                                    |

| SECTION 2 | DESCRIPTION, OPERATION AND MAINTENANCE                                                                                                                                                                                                                            |                                                                                    |

| CHAPTER 1 | GENERAL DESCRIPTION                                                                                                                                                                                                                                               | 1-1                                                                                |

| CHAPTER 2 | OPERATING INSTRUCTIONS Power Supply Frequency Measurement Period Measurement Time Interval (TI and TI Average) Ratio Totalize Battery Economy Operation Standby Operation with AC Power Battery Charging Description of Controls                                  | 2-1<br>2-1<br>2-2<br>2-3<br>2-5<br>2-5<br>2-7<br>2-7<br>2-7<br>2-8                 |

|           | Indicators<br>Rear Panel Items                                                                                                                                                                                                                                    | 2-12<br>2-13                                                                       |

| CHAPTER 3 | PRINCIPLES OF OPERATION The CDI Chip General Circuit Functions Self Check Average Period Measurement Time Interval (Single Line) Time Interval (Double Line) Time Interval Average Ratio Totalize Control Sequence Display and Data Output System Resistor Arrays | 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11 |

Contents (1)

|           |                                                 | Page                         |

|-----------|-------------------------------------------------|------------------------------|

| CUARTER A | TECHNICAL DESCRIPTION                           |                              |

| CHAPTER 4 | Introduction                                    | 4-1                          |

|           |                                                 | 4-1                          |

|           | Logic Circuit Symbols                           | 4-1                          |

|           | Operating Controls                              | 4-1                          |

|           | Function and Range Switching Switch Selection   |                              |

|           | Control Codes                                   | 4-1<br>4-1                   |

|           |                                                 | 4-1                          |

|           | Data Latch/Unlatch                              | 4-3<br>4-3                   |

|           | CHECK/OPERATE/HOLD and RESET                    | 4 <b>-</b> 3                 |

|           | A Channel Input                                 | 4 <b>-</b> 3                 |

|           | A Channel AC Amplifier                          | 4-4                          |

|           | DC Amplifiers                                   | 4-4                          |

|           | B Channel Amplifier                             | 4 <b>-</b> 4<br>4 <b>-</b> 5 |

|           | Signal Selection                                | 4 <b>-</b> 5                 |

|           | Slope Selection<br>Start Inhibit                | 4 <b>-</b> 5                 |

|           | Stop Channel Selection                          | 4 <b>-</b> 6                 |

|           | •                                               | 4 <b>-</b> 6                 |

|           | Hold Off and Hold Off Display                   | 4 <b>-</b> 8                 |

|           | Manual Start and Stop                           | 4 <b>-</b> 7                 |

|           | Data Output and Display                         | 4 <b>-</b> 7<br>4 <b>-</b> 7 |

|           | Decimal Point Decoding Overflow                 | 4-7<br>4-8                   |

|           |                                                 | 4 <b>-</b> 8                 |

|           | Gate Indicator                                  | 4 <b>-</b> 8                 |

|           | Units Indicators                                | 4-8<br>4-8                   |

|           | Display Time and Reset Generator                | 4-8<br>4-8                   |

|           | Introduction                                    | 4-8<br>4-8                   |

|           | Display Time Circuit Reset Pulse and Hold State | 4-9                          |

|           | Manual Reset                                    | 4-9<br>4-9                   |

|           | External Reset                                  | 4-9<br>4-9                   |

|           |                                                 | 4-9<br>4 <b>-</b> 9          |

|           | Segment Check                                   | 4-9<br>4-9                   |

|           | Frequency Standard                              | 4-9                          |

|           | Oscillator Assembly 11-1254                     | 4-10                         |

|           | Precision Oscillators                           | 4-10                         |

|           | Frequency Doubler                               | 4-10<br>4-10                 |

|           | 1 MHz Standard Output External Standard Input   | 4-10<br>4-10                 |

|           | CATHOLIST MULTURALISM ILICALISM                 | ## III                       |

Contents (2)

|           |                                         | Page          |

|-----------|-----------------------------------------|---------------|

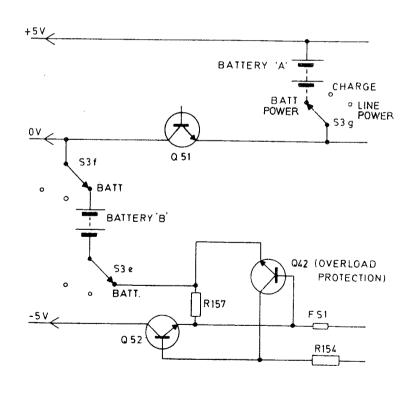

|           | Power Supply                            | 4-11          |

|           | Introduction                            | 4-11          |

|           | Line Power                              | 4-11          |

|           | +5V Switching                           | 4-11          |

|           | Standby Indicator LP1                   | 4-11          |

|           | +5V Stabilization                       | 4-12          |

|           | -5V Stabilization                       | 4-12          |

|           | Battery Economy Operation               | 4-13          |

|           | Battery Charging                        | 4-13          |

|           | Charge Indicator LP3                    | 4-14          |

|           | Battery Powered Operation               | 4-14          |

|           | Battery Low Indicator LP2               | 4-15          |

|           | Over Discharge Protection               | 4-15          |

|           | CDI Chip Stabilized Supply              | 4-15          |

| CHAPTER 5 | MA INTENA NCE                           |               |

| •         | Test Equipment Required                 | 5-1           |

|           | Removal of Covers                       | 5-2           |

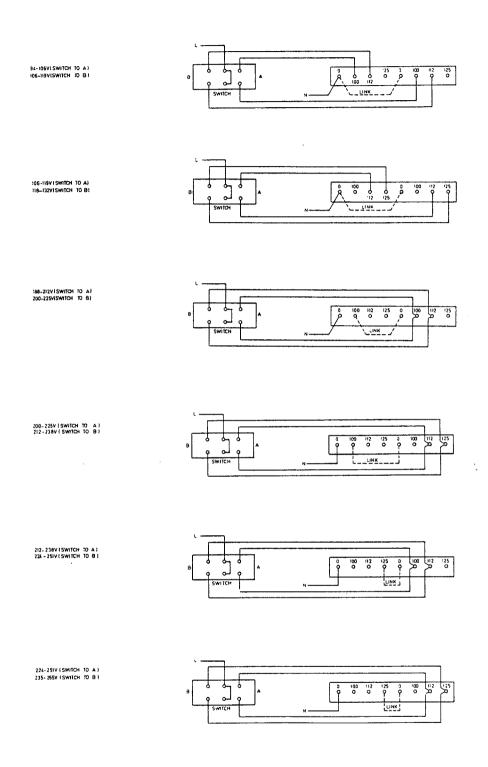

|           | Transformer Voltage Selection           | 5-2           |

|           | Fuses                                   | 5 <b>-</b> 2  |

|           | Power Lead                              | 5-4           |

|           | AC Power Supplies Check                 | 5-4           |

|           | Resistance Check                        | 5 <b>-</b> 4  |

|           | Supply Rail Voltages                    | 5-4           |

|           | Ripple Level                            | 5 <b>-</b> 5  |

|           | Battery Power Supplies Check            | 5-5           |

|           | Charging Rate Checks                    | 5 <b>-</b> 5  |

|           | Battery Economy Check                   | 5 <b>-</b> 6  |

|           | Performance Tests and Calibration       | 5 <b>-</b> 6  |

|           | Segment, Decimal Point and Self Check   | 5 <b>-</b> 6  |

|           | AC Sensitivity Check, Input A           | 5 <b>-</b> 7  |

|           | Totalize Check                          | 5-9           |

|           | DC Amplifier and Attenuator Checks      | 5-10          |

|           | Ratio Check                             | 5-10          |

|           | Time Interval, Single Line Check        | 5-11          |

|           | Time Interval, Double Line Check        | 5-13          |

|           | Time Interval, (Average) Check          | 5-14          |

|           | DC Offset Check                         | 5-15          |

|           | External Frequency Standard Check       | 5-16          |

|           | Internal Frequency Standard Calibration | 5 <b>-</b> 17 |

|           | Dismantling and Reassembly              | 5 <b>-</b> 18 |

|           | Removal of Display PCB                  | 5-18          |

|           | Removal of Main PCB                     | 5 <b>-1</b> 9 |

|           | Fitting Frequency Standard 9421 or 9442 | 5 <b>-</b> 19 |

|           | Fitting Battery Pack 11–1289            | 5-20          |

# IN TEXT ILLUSTRATIONS

| Fig.No.    |                                                   | Page           |

|------------|---------------------------------------------------|----------------|

| A.1        | Data Sequence Diagram                             | Tech.Spec (12) |

| 3.1        | Basic Frequency Meter                             | 3-1            |

| 3.2        | Period Measurement                                | 3-4            |

| 3.3        | Time Interval Measurement                         | 3-5            |

| 3.4        | Time Interval (Average) Measurement               | 3-6            |

| 3.5        | Ratio Measurement                                 | 3 <b>-</b> 7   |

| 3.6        | Totalize                                          | 3 <b>-</b> 8   |

| 3.7        | Control Sequence                                  | 3-9            |

| 3.8        | Multiplex Display System                          | 3-10           |

| 5.1        | Voltage Selection Diagram                         | 5 <b>-</b> 3   |

|            | LIST OF TABLES                                    |                |

| Table No.  |                                                   | Page           |

| 1          | Data Output Socket                                | Tech.Spec.(10) |

| 2<br>3     | Function Information                              | Tech.Spec.(11) |

| 3          | Time Base Selection                               | Tech.Spec.(11) |

| <b>4</b> a | Function Information                              | 4-2            |

| 4b         | Time Base Selection                               | 4-2            |

| 5          | Test Equipment Required                           | 5-1            |

| 6          | Power Supply Resistance Measurement               | 5-4            |

| 7          | Self Check Readout                                | 5 <b>-</b> 7   |

| 8          | Input 'A' Sensitivity Checks                      | 5 <b>-</b> 8   |

| 9          | Time Interval Decimal Point Check                 | 5-12           |

| 10         | Slope Selection Switch Check                      | 5-13           |

| 11         | Time Interval (Average) Check                     | 5-15           |

| SECTION 3  | PARTS LISTS, COMPONENT LAYOUTS AND                |                |

|            | CIRCUIT DIA GRAMS                                 |                |

|            | Component Layout: Display Assembly                | Fig.1          |

|            | Parts List 1: Display Assembly                    |                |

|            | Circuit and Component Layout: Oscillator Assembly | Fig.2          |

|            | Parts List 2: Oscillator Assembly 11-1254         |                |

|            | Parts List 3: Chassis, Front and Rear Panels      |                |

|            | Parts List 4a and 4b: Main PCB Assembly           |                |

|            | Component Layout: Main PCB Assembly               | Fig.3          |

| ·<br>·     | Overall Circuit: 9904                             | Fig.4          |

|            |                                                   |                |

SECTION 4

APPENDICES AND CHANGE INFORMATION

OPTION 01:

Serial to Parallel Interface

Unit

Appendix 1

9904 Vol.2

# SECTION 1 TECHNICAL SPECIFICATION

# TECHNICAL SPECIFICATION

GENERAL 1.

Model 9904 is a seven digit 50 MHz Universal

Counter Timer.

MEASURING FUNCTIONS 2.

The modes of operation are:-

Frequency

Single and Multiple Period (2)

Single and Multiple Ratio (3)

(4) Single and Double Line Time Interval

Single and Double Line Time Interval Averaging

(6) Totalizing

DISPLAY 3.

Format:

Seven digit in-line, seven segment I.e.d. display. The decimal point positioning is automatic.

Latch:

The display is latched for Frequency, Period and Ratio measurement, and automatically unlatched in all other modes.

Display Time:

Gate time + 0.15s in Frequency, Period and

Ratio modes.

1.5s in other modes.

A switched HOLD position is provided.

Measurement Check:

Counter reads 1 MHz.

Segment Check:

Sets all numerical indicators to 8.

Reset:

Normally automatic, but a push-button for manual operation is provided.

Overflow/Standby Indicator:

Lights when overflow occurs or when instrument

is in the Standby mode.

Gate/Charging Indicator:

Lights when the main gate is open or when the internal batteries are on full charge rate.

Battery Low Indicator:

Lights when internal batteries require charging.

Units Indicators:

Light to indicate the appropriate units for

the display.

External Standard Indicator:

Lights when the instrument is operating from

an external standard.

## 4. CHANNEL 'A' INPUT - AC COUPLED

Frequency Range:

10 Hz to 50 MHz.

Sensitivity:

10mV r.m.s. A variable sensitivity control

is provided.

Maximum Signal Level:

250 V r.m.s. up to 20 kHz. 50 V r.m.s. up to 100 kHz. 10 V r.m.s. above 100 kHz.

Maximum Input Level:

The d.c. level + peak signal level must not exceed 400V over the full frequency range.

Input Impedance:

1 M $\Omega$  in parallel with approximately 25 pF, falling to  $100k\Omega$  at 4V r.m.s. with sensitivity

control in 10mV position.

#### 5. CHANNELS 'A' and 'B' - DC COUPLED

Frequency Range:

'A' Channel: d.c. to 20 MHz.

'B' Channel: d.c. to 10 MHz.

Pulse Duration:

25ns minimum at trigger points.

Trigger Levels:

± 3V or ± 30V nominal, with switched zero

offset position.

Trigger lamps flash to indicate when the input level is passing through the input

hysteresis threshold.

Sensitivity:

± 140mV about offset level for ± 3V offset. + 1.4V about offset level for ± 30V offset.

Attenuator:

X10 attenuator selected by front panel switches, giving increased offset with

reduced sensitivity.

Input Impedance:

With attenuator at X1:

1MΩ in parallel with approximately 25pF,

falling to  $100k\Omega$  at  $\pm 5V$  r.m.s.

With attenuator at X10:

1MΩ in parallel with approximately 25pF,

falling to  $900k\Omega$  at  $\pm 50V$  r.m.s.

Maximum Input Level:

With attenuator at X1:

100V r.m.s. up to 1 MHz, decreasing to

10V r.m.s. at 20 MHz. With attenuator at X10:

100V r.m.s. up to 1 MHz, decreasing to

40V r.m.s. at 20 MHz.

Hold Off:

Permits inhibition of the stop signal in

Time Interval and Totalize modes for a period

variable from 0.1 to 100ms.

The delay can be displayed by selecting

CHECK and Time Interval mode.

Start Inhibit:

Permits inhibition of the start signal in

Time Interval and Totalize modes.

6. FREQUENCY MEASUREMENT

Input Channel:

Channel 'A'

Coupling:

AC or DC

Frequency Range:

AC coupled: 10Hz to 50MHz

DC coupled: d.c. to 20MHz

Gate Times:

1 ms to 100s in decade steps.

Accuracy:

± 1 count ± frequency standard accuracy. \*

7. SINGLE AND MULTIPLE PERIOD MEASUREMENT

Input Channel:

Channel 'A'

Coupling:

AC or DC

Range:

1µs to 10s

Clock Unit:

lµs

Periods Averaged:

1 to  $10^5$  in decade multiples.

Accuracy:

$\pm 0.3\%$

Number of periods averaged ± frequency

standard accuracy ± 1 count.

(at 50 mV r.m.s. input with 40 dB S/N ratio)

Bandwidth:

Automatically reduced to 10MHz (3dB) when

on AC and Period mode is selected.

#### 8. TIME INTERVAL - SINGLE AND DOUBLE LINE

Input Channel:

Single Line: Channel 'B'

Double Line: Start Channel 'B'

Stop Channel 'A'

Time Range:

100ns to 10<sup>5</sup>s (28 hours)

Clock Units:

100ns to 10ms

Start and Stop Signals:

Electrical or contact.

Manual Start and Stop:

By single push button on front panel.

Trigger Slope Selection:

Electrical: positive or negative slopes of both Start and Stop signals can be selected.

Accuracy:

± 1 count ± trigger error ± frequency

standard accuracy.

Trigger error:

(in ns)

Signal slope at trigger point (V/µs)

#### 9. TIME INTERVAL AVERAGING - SINGLE AND DOUBLE LINE

Input Channel:

Single Line: Channel 'B'

Double Line: Start Channel 'B'

Stop Channel 'A'

Time Range:

150ns to 1s

Dead Time Between Intervals:

150ns minimum

Clock Unit:

100ns

Time Interval Averaged:

1 to  $10^5$  in decade multiples.

Accuracy

± Frequency standard accuracy ± system error

± averaging error.

System error: 10ns maximum per input channel. This is the difference in delays between start and stop signals and can be minimised by

matching externally.

Averaging error: Trigger Error + 100 √Intervals Averaged

Trigger error: Signal slope at trigger point (V/us)

10. **RATIO**

Higher Frequency Input:

Channel 'A': AC coupled; 10Hz to 50MHz DC coupled; d.c. to 20 MHz

Lower Frequency Input:

Channel 'B': d.c. to 10MHz.

Accuracy:

± 1 count ± trigger error on Channel 'B'

Reads:

Frequency A Frequency B

Multiplier n

$1 \text{ to } 10^5 \text{ in decade multiples.}$

11. TOTALIZING

Input Channel:

Channel 'A': d.c. to 10MHz.

Maximum Rate:

10<sup>7</sup> events per second.

Pulse Width:

50ns minimum at trigger points.

Prescaling:

Events can be prescaled in decade multiples

(n) from 1 to 10<sup>3</sup>.

Reads:

Number of input events + 1 count

Manual Start and Stop:

By single push button on front panel.

Electrical Start and Stop:

By electrical signal applied to Channel 'B'.

12. FREQUENCY STANDARD

Frequency:

5 MHz

Type:

Refer to Options 04A, 04B and 04C on page

Tech.Spec.(7).

Frequency Standard Output:

A 1 MHz rectangular waveform is available at the rear panel BNC socket. This is t.t.l. compatible (600mV peak to peak into  $50\Omega$ ).

#### 13. EXTERNAL FREQUENCY STANDARD

Frequency:

1 MHz

Waveform:

Sinewave or pulse (up to 4:1 mark/space ratio).

Input Socket:

Applied to the Channel 'B' input. Provides an external standard for Frequency and Period measurement only.

Indicator:

A front panel I.e.d. lights when the external standard is present. Change over from internal to external standard is automatic.

#### - 14. EXTERNAL SIGNALS

Data Output:

Eight digits with overflow and decimal point in serial BCD form at standard t.t.l. level. Refer to Supplementary Data on page Tech. Spec. (10).

Other Outputs:

See Supplementary Data on page Tech. Spec. (10).

Inputs:

Reset and print hold.

#### 15. POWER REQUIREMENTS

Voltage Ranges(a.c.)

Appropriate transformer connections allow six pairs of voltage ranges to be selected. A rear panel switch selects either the upper or lower range of each pair.

- (1) 94-106V/106-119V

- (2) 106-119V/118-132V

- (3) 188-212V/200-225V

- (4) 200-225V/212-238V

- (5) 212-238V/224-251V

- (6) 224-251V/235-265V

Refer to Chapter 5 for setting instructions.

Frequency:

45 to 450 Hz.

Consumption:

19VA approximately.

# 16. ENVIRONMENTAL & SAFETY SPECIFICATIONS

Operating Temperature Range:

0°C to +55°C (to +40°C with Battery Option)

Storage Temperature Range:

-40°C to +70°C (to +60°C with Batteries)

Humidity:

95% r.h. at +40°C.

Mechanical:

Tested in accordance with IEC 68. (BS2011

recommendations).

Safety:

Meets IEC 348 (BS4743) recommendations.

#### 17. MECHANICAL

Dimensions:

Height: 83 mm (case only)

110 mm overall

Width: 240 mm (case only)

284 mm overall

Depth: 268 mm

Weight:

2.7kg (excluding battery pack)

Battery pack 1.5kg.

# 18. OPTION 01 SERIAL TO PARALLEL INTERFACE

Data Control Information:

8 decades of data in 4 line BCD weighted 1248, 3 line decimal point position, print command, print hold, reset, overflow and time-base information. All logic levels are t.t.l.

compatible.

# 19. OPTION 04A FREQUENCY STANDARD 9442

Type:

A fast warm up, ovened precision oscillator

suitable for the majority of operations.

Frequency:

5MHz.

Ageing Rate:

$\pm 3$  parts in  $10^9$ /day averaged over a minimum

of 10 days after 3 months continuous

operation.

Warm-up Time:

Better than  $\pm 2$  parts in  $10^7$  within 6 minutes.

Temperature Stability:

Better than ± 3 parts in 10<sup>9</sup> per °C over the range -10°C to +45°C, but operable to +55°C.

#### 20. **OPTION 04B FREQUENCY STANDARD 9421**

Type: An ovened oscillator of the utmost precision

for use when the highest long term accuracy is essential. Not available when the Battery

Pack option is fitted.

Frequency:

5 MHz.

Ageing Rate:

± 2 parts in 10<sup>9</sup> per day averaged Initial:

over a minimum of 10 days at

shipment.

Long Term:  $\pm 5$  parts in  $10^{10}$ / day averaged

over a minimum of 10 days after 3 months continuous operation.

Warm-up Time:

Better than  $\pm 1$  part in  $10^7$  within 20 minutes.

Temperature Stability:

Better than  $\pm$  6 parts in  $10^{10}$  per  $^{\circ}$ C averaged over the range  $-10^{\circ}$ C to  $+45^{\circ}$ C, but operable

to +55°C.

#### 21. OPTION 04C FREQUENCY STANDARD 11-1254

Type: An unovened crystal oscillator for non-

critical applications or where an external

house standard is to be used.

Frequency:

5MHz.

Temperature Stability:

$\pm$  8 parts in  $10^6$  over temperature range  $0^{\circ}$ C to  $\pm$ 55 °C.

± 3 parts in  $10^6$  over temperature range +20°C

Average Ageing Rate:

± 1 part in 10<sup>6</sup> per month three months after

delivery but less than  $\pm 1$  part in  $10^5$ , in the

first year.

#### 22. BATTERY POWER PACK OPTION: II-1289

Mechanical: The battery pack is mounted on a metal tray

> inside the instrument, and connected via a polarised 4 pin connector to the main p.c.b.

Selection: By means of 3 position LINE POWER/CHARGE/

BATTERY POWER switch on rear panel.

Battery Life:  $4\frac{1}{2}$  hours minimum continuous operation at

+20°C, 15 hours minimum on standby at +20°C.

**Battery Condition Indicator:** A front panel I.e.d. lights when batteries

require charging.

14 hours at +20°C. Charge Time:

Standby Facility: With the NORMAL/STANDBY switch in

> STANDBY position only the internal standard is operational. Pressing the RESET button activates the counter for approximately one minute, after which it reverts to the standby

condition.

23. **ACCESSORIES**

> Accessories Supplied: Operators Handbook

> > Spare fuses.

Accessories Available: Rack mounting kit (11-1126)

> Rigid carrying case (15-0450) Padded carrying case (15-0444) Data output connector (23-5147)

#### SUPPLEMENTARY DATA

#### DATA OUTPUT CONNECTIONS

A1. Data and command information is provided on a 28-way edge connector accessible via a removable cover on the rear panel. The facilities and pin connections are listed in Table 1 below. The logic for time base and function data is given in Tables 2 and 3.

TABLE 1

Data Output Socket

| Pin | Facility                      | Pin | Facility                      |

|-----|-------------------------------|-----|-------------------------------|

| 1   | -5V (nominal)                 | Α   | 0V                            |

| 2   | +5V (nominal)                 | ٧   | Overflow (static indication)  |

| 3   | Key Way                       | С   | Key Way                       |

| 4   | 4 (BCD)                       | D   | Ī (BCD)                       |

| 5   | 8 (BCD)                       | E   | 2 (BCD)                       |

| 6   | External Hold Input           | F   | 10kHz Sync.                   |

| 7   | External Reset Input          | Н   | Main Gate                     |

| 8   | Not Used                      | j   | Start Inhibit                 |

| 9   | _<br>c ) Function             | K   | _<br>z ) Time Base            |

| 10  | b ) Information (See Table 2) | L   | y ) Information (See Table 3) |

| 11  | a )                           | M   | (Jee Tuble 3)                 |

| 12  | $\overline{R(O)}$             | N   | Not Used                      |

| 13  | Hold/Reset                    | P   | Not Used                      |

| 14  | Not Used                      | R   | Not Used                      |

# NOTES 1 External Hold Input

To extend the cycle time the external hold signal (logic '0') must be applied during the gate or hold time. To initiate a new measurement cycle the external hold must go 'high' for not less than  $200\mu s$ .

### 2 External Reset Input

To apply external reset the level at pin 7 must go to logic '0' for not less than 5ms. On reverting to '1' level the display resets to 'all zeros' and a new measurement commences.

# FUNCTION AND TIMEBASE LOGIC CODES

#### **Function Data**

A2. Function information format: 3 lines coded as shown. The table gives the logic available at the edge connector. The inverse levels are applied to the CDI Chip in the instrument.

TABLE 2

Function Information

| FUNCTION                                      | ā | Code<br>b | -<br>- |

|-----------------------------------------------|---|-----------|--------|

| Frequency                                     | 1 | ]         | 1      |

| Average Period                                | 0 | I         | 1      |

| Totalize <u>A</u><br>n                        | 0 | 1         | 0      |

| Ratio <u>A</u><br>n <u>B</u>                  | 1 | 1         | 0      |

| T.I.(single line or double line not averaged) | 0 | 0         | 1      |

| T.I.(single line or double line averaged)     | 1 | 0         | 7      |

# Time Base Selection Data Output

A3. Time Base information: 3 lines coded as shown. The inverse levels are applied to the CDI Chip in the instrument.

TABLE 3

Time Base Selection

| _<br>× | <u>C</u> ode<br>У | _<br>z | Frequency<br>Gate Time | Multiplier<br>'n' | Time Interval<br>Clock |

|--------|-------------------|--------|------------------------|-------------------|------------------------|

| 1      | 1                 | 1      | lms                    | 1                 | 0.1µs                  |

| 0      | 1                 | ו      | 10ms                   | 10 <sup>1</sup>   | lμs                    |

| 1      | 0                 | 1      | 100ms                  | 10 <sup>2</sup>   | 10 <sub>µ</sub> s      |

| 0      | 0                 | 1      | l sec                  | 10 <sup>3</sup>   | 100µs                  |

| 1      | 1                 | 0      | 10sec                  | 10 <sup>4</sup>   | 1 ms                   |

| 0      | 1                 | 0      | 100sec                 | 10 <sup>5</sup>   | 10ms                   |

### DATA OUTPUT FORMAT

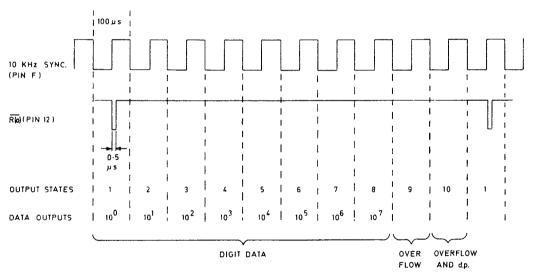

- A4. In standard format the b.c.d. output data is available at the 28-way edge connector in a bit parallel byte serial form. The data is sequenced by a 10 kHz synchronising signal. The data presentation is delayed 0.5µs from the negative edge of the synchronising signal. An additional synchronising pulse R(0) determines the first state (10° digit). Accessories are available to give data output in parallel form (for printers etc.) or IEC/ASCII bus compatible format.

- A5. The ten data output states are as follows: the timing is shown in the diagram.

| States | <u>Facility</u>                                                                                      |

|--------|------------------------------------------------------------------------------------------------------|

| 1 to 8 | Digit (display information).                                                                         |

| 9      | Overflow for $10^3$ , $10^4$ , $10^6$ and $10^7$ digits on pins D, E, 4 and 5 respectively.          |

| 10     | Decimal point position in kHz units, plus overflow information for 10 <sup>5</sup> digit, via pin 5. |

Data Sequence Diagram

Fig A.1

# SECTION\_2

# DESCRIPTION

OPERATION & MAINTENANCE

#### CHAPTER 1

## GENERAL DESCRIPTION

#### INTRODUCTION

1.1 The 9904 is a seven-digit universal counter timer, powered from a.c. line power or optional internal batteries and with a comprehensive range of facilities.

#### **OPERATING FACILITIES**

- 1.2 (a) Frequency measurement ranges: AC coupled: 10 Hz to 50 MHz.

DC coupled: DC to 20 MHz.

- (b) Period measurement, 1 to 10<sup>5</sup> periods in decade steps, a.c. or d.c. coupled.

- (c) Ratio measurement.

- (d) Time Interval, single or double line, with manual or electrical start/stop signals, trigger slope selection.

- (e) Time Interval average, single or double line, with trigger slope selection.

- (f) Totalize, with electronic or manual start/stop.

- In addition to the usual control facilities such as AC/DC input selection, manual Hold and Reset, Check etc., the 9904 incorporates variable a.c. sensitivity on the 'A' channel and variable d.c. offset on both 'A' and 'B' channels. Variable hold-off protection is available when using Time Interval or Totalize mode. The amount of hold-off (in milliseconds) can be displayed.

#### POWER SUPPLY

## AC (Line Power) Supply

1.4 The instrument operates from a.c. supplies between 94 and 265 volts, 45 to 450 Hz. Tappings and a link on the line power transformer provide a choice of six voltage ranges. A rear panel switch allows selection of the upper or lower half of the chosen range. A label fixed to the rear panel should indicate the chosen range. Spare labels for ranges other than 212 to 251 V are supplied.

#### Battery Power Supply (Option)

1.5 The instrument can operate either from line power supplies, or from an internal battery pack containing re-chargeable nickel cadmium cells. The batteries allow  $4\frac{1}{2}$  hours continuous operation from the full charged condition. A 3-position rear panel switch selects line or battery power, or full-rate charging of the batteries from the internal charging circuit. When on battery operation a warning light indicates when battery voltage is low.

## **Battery Charging**

1.6 To fully charge a discharged battery requires 14 hours. Avoid overcharging as it will progressively reduce battery charge capacity. When the instrument is operating from line power supply the batteries receive a trickle charge which can continue indefinitely without detriment to the batteries.

#### Battery Economy (Standby) Facility

1.7 This facility may be used when continuous readout is not required. On BATTERY operation with the front panel POWER switch at STANDBY, the instrument is 'off' except for the internal frequency standard. If the RESET button is depressed and released the instrument will then operate normally for approximately one minute, after which it reverts to the standby condition. This operation may be repeated as required.

#### FREQUENCY STANDARD

- 1.8 At the customer's option one of three 5MHz oscillators from the Racal-Dana range can be fitted. Details will be found in the Technical Specification.

Option 04C is a discrete component oscillator, and a parts list and circuit will be found in Section 3 of this manual. Options 04A and 04B should be serviced only by Racal-Dana Instrument Ltd., or their agents. For all options an aperture in the rear panel provides access for calibration.

- 1.9 An external standard, which will automatically over-ride the internal standard, can be applied via the front panel 'B' input socket for use in the Frequency and Period modes. A front panel I.e.d. lights when the external standard is operating.

- 1.10 A 1 MHz reference, derived from the standard in use, is available at the rear panel BNC socket.

#### CARRYING HANDLE

The instrument is fitted with a combined carrying handle and bench stand.

To adjust the stand, press in the two handle bosses simultaneously, while setting the stand to the desired position.

#### OPERATORS MANUAL

1.12 A separate Operators manual is supplied with each instrument.

# CARRYING CASE AND RACK MOUNTING

1.13 A rigid carrying case (Part No. 15-0450) and a 19-inch rack mounting kit (Part No. 11-1126) are available to order.

## CHAPTER 2

#### OPERATING INSTRUCTIONS

#### POWER SUPPLY

2.1 Line Power. Before operating a new instrument or at a new location, check that the line voltage selection and fuse rating are correct (see rear panel label). Set the rear panel switch to LINE POWER:

Battery Supply (Option). Set the rear panel switch to BATTERY POWER. Set the POWER switch to ON and verify that the BATTERY LOW indicator is not illuminated.

#### FREQUENCY MEASUREMENT

- 2.2 In this mode the unknown frequency is gated to the counter decades for the gating period selected by the chosen Time Base (n) push button. For frequencies below 10 kHz the use of period mode will give greater resolution.

- (1) Set the POWER switch to ON and the Normal/Standby switch to NORMAL.

- (2) Set the following controls:-

- (a) Function switch to FREQUENCY 'A'.

- (b) AC/DC switch to AC or DC, as required.

- (c) If using AC mode set the SENSITIVITY control initially to the maximum clockwise position.

- (d) If using DC mode set the same control to the '0' (switched) position (fully anti-clockwise), and the 'A' Channel Attenuator to X1 or X10.

- (e) CHECK/OPERATE/HOLD switch to OPERATE.

- (3) Connect the unknown signal to the 'A' input socket.

- (4) Select the required Time Base (n) push-button.

- (5) If using AC mode adjust the SENSITIVITY control anti-clockwise to to obtain stable counting. If using DC mode adjust the same control for the required d.c. triggering level.

- (6) Switching to HOLD stops the automatic updating of the display. A 'one shot' update can be obtained by pressing and releasing the RESET button.

Time Base Range Selection Frequency Mode)

| Gate Opening Time | Multiplier 'n'  | Display Resolution |

|-------------------|-----------------|--------------------|

| 1 ms              | 7               | 1 kHz              |

| 10 ms             | 10              | 100 Hz             |

| 100 ms            | 10 <sup>2</sup> | 10 Hz              |

| l s               | 10 <sup>3</sup> | 1 Hz               |

| 10 s              | 104             | 0.1 Hz             |

| 100 s             | 10 <sup>5</sup> | 0.01 Hz            |

#### Overflow Procedure

2.3 To obtain high resolution when measuring high frequencies it may be advantageous to 'overspill' one or more of the left-hand digits. First of all, select a short gate time and record the most significant digits displayed, then select a Range button giving a longer gate time to display the less significant digits to the required resolution.

#### PERIOD MEASUREMENT

This mode is recommended for measuring low frequencies in the range of 10 Hz to 10 kHz with improved resolution. The incoming signal is taken to the time-base decade dividers, the output of which (selected by the Time Base (n) push-button) gates the internal reference frequency to the counter decades. The display indicates the actual value of the period of the incoming signal in microseconds. Greater accuracy is obtained by selecting a longer time base range thus taking the measurement over a greater number of periods.

#### Period Operation

- 2.5 (I) Set the POWER switch to ON and the NORMAL/STANDBY switch to NORMAL.

- (2) Set the following controls:-

- (a) Function switch to PERIOD 'A'.

- (b) AC/DC switch to AC or DC, as required.

- (c) If using AC mode, set the SENSITIVITY control initially to maximum clockwise.

- (d) If using DC mode set the same control to zero offset, '0' (switched) position, and the 'A' Channel Attenuator to X1 or X10 as required.

- (e) CHECK/OPERATE/HOLD switch to OPERATE.

- (3) Connect the unknown signal to the 'A' input socket.

- (4) Select the number of cycles to be timed by depressing the relevant Time Base (n) push-button. A greater number of cycles gives enhanced resolution but longer measuring time.

- (5) If on AC mode adjust the SENSITIVITY control anti-clockwise for stable counting. If on D.C. mode adjust the same control to the required DC offset. For zero offset set the control to '0' (switched) position.

- (6) Switching to HOLD stops the automatic updating of the display A 'one-shot' update can be obtained by pressing releasing the RESET button.

#### TIME INTERVAL (T.I. and T.I. Average)

- 2.6 In this mode the instrument is effectively serving as a stop-watch by counting clock pulses derived from the frequency standard. The time interval may be controlled by successive events on a single line in which case Input 'B' is used with the Stop Channel Selection switch set to 'B'.

- 2.7 For timing events on separate lines the Stop Channel Selection switch must be set to 'A'. The 'start' signal is applied to the 'B' Input and the 'stop' signal to the 'A' input. Trigger slopes can be selected by the START/STOP slope switches. On T.I. signals at the STOP input can be inhibited by use of the HOLD OFF control.

- 2.8 The T.I. mode is most suited to the measurement of single intervals such as pulse widths. A range of widths from 100 ns to several hours may be measured by selecting the appropriate clock unit.

The maximum clock rate is 100 ns, therefore resolution on short duration pulses is likely to be unsatisfactory, but can be improved by the use of T.I. Average mode, which increases resolution by the averaging of the inherent  $\pm 1$  count 'gate uncertainty' factor over a number of time intervals (1 to  $10^5$ ). It should be noted, when time averaging, that the repetition rate of the pulses under measurement must not be harmonically related to the frequency standard in use.

#### Time Interval Operation

- 2.9 (1) Set the POWER switch to ON and the NORMAL/STANDBY switch to NORMAL.

- (2) Set the following controls:-

- (a) Function: depress the T.I. or T.I. Avg\* button, as required.

- (b) On T.I.: HOLD OFF control as required.

- \*NOTE: On Time Interval Average (single line) the \_r to \_r and \_ to \_ measurement is effectively equivalent to Period mode. Therefore the user is recommended to use Period for this particular type of measurement as the accuracy is greater and the measurement time reduced.

- (c) Stop Channel Selection switch: for single line select B'. For double line select A and set the 'A' Channel AC/DC switch to DC.

- (d) START and STOP switches: select required triggering polarities. (Not required for manual timing).

- (e) Attenuator X1/X10 as required.

- (f) CHECK/OPERATE/HOLD switch to OPERATE.

- (3) Connect the input(s). For single line timing connect the external signals to Input 'B'. For double line connect the 'start' line to 'B' and the stop line to 'A'.

- (4) Press the Time Base (n) button which provides the appropriate readout. One of the I.e.d. indicators will light to indicate the units of the display.

- (5) For manual timing (on T.1. only) press and release the START/STOP push-button as required.

- (6) Switching to HOLD stops the automatic updating of the display. A 'one shot' update can be obtained by pressing and releasing the RESET button.

# RATIO $n\frac{A}{B}$

2.10 In this mode, two unknown signals are fed to inputs 'A' and 'B'. Generally the higher frequency is fed via input socket 'A' to the counter decades and the lower frequency is fed through input socket 'B' to the time-base decades, but this input arrangement may be reversed, as for example, when the lower frequency has a smaller amplitude (e.g. 10 mV) and the higher frequency a considerably larger amplitude. The display indicates the ratio  $\frac{A}{B}$  and the reading must be divided by the factor 'n' to obtain the ratio  $\frac{A}{B}$ .

### Ratio Operation

- 2.11 (1) Set the POWER switch to ON and NORMAL/STAN DBY switch to NORMAL.

- (2) Set the following controls:-

- (a) The FUNCTION switch to RATIO n  $\frac{A}{B}$

- (b) The AC/DC switch to AC or DC as appropriate.

- (c) Attenuators X1/X10 as required.

- (d) CHECK/OPERATE/HOLD switch to OPERATE.

- (3) Connect the input signals to sockets 'A' and 'B'. (See para.2.10).

- (4) Set Trigger Level controls as required.

- (5) Press the Time Base button which gives a full display without overspill.

- (6) Switching to HOLD stops the automatic updating of the display. A 'one shot' update can be obtained by pressing and releasing the RESET button.

- (7) To obtain the true ratio the displayed reading must be divided by the factor 'n' indicated above the selected Time Base push button.

# TOTALIZE $\frac{A}{n}$

### Theoretical Considerations.

2.12 In this mode, signals on the 'A' input socket are prescaled and taken to the counter decades. The count can be controlled manually by the START/STOP button or electrically by timing signals connected to the 'B' input socket. This mode permits a number of events occurring with random timing to be counted over a chosen period.

A counter time base in Totalize mode is generally designed to reset to either 0 or 9; in either case a rounding off of the count occurs to an accuracy of  $\pm 1$  count, as shown in the following table. It should be noted that the Racal counter 9904 resets to 9.

| No. of i/p pulses (n = 10 <sup>3</sup> selected) | Counter     | Display     | Error   |         |  |  |  |  |

|--------------------------------------------------|-------------|-------------|---------|---------|--|--|--|--|

| (n = 10 <sup>3</sup> selected)                   | t/b reset 9 | t/b reset 0 | Reset 9 | Reset 0 |  |  |  |  |

| 1                                                | 1           | 0           | 0.999   | 0.001   |  |  |  |  |

| 999                                              | 1           | 0           | 0.001   | 0.999   |  |  |  |  |

| 1000                                             | 1           | 1           | 0       | 0       |  |  |  |  |

NOTE: Using  $n = 10^3$  the error of  $\pm 1$  count is relative to 'n minus one' input pulses (i.e. 999 pulses). For full resolution n = 1 could have been selected, then the error of  $\pm 1$  count would have been related to the display or the number of input pulses (i.e. 1 pulse).

Thus an increase in n division will give increase in counter range, but a decrease in resolution.

### Totalize Operation

- 2.13 (1) Set the POWER switch to ON and NORMAL/STANDBY switch to NORMAL.

- (2) Set the following controls:-

- (a) The Function switch to TOTAL  $\frac{A}{n}$

- (b) The Stop Channel Selection switch to 'B'.

- (c) Attenuators X1/X10 as required.

- (d) The 'A' Channel AC/DC switch as required.

- (e) The HOLD OFF control as required.

- (f) The START and STOP switches to select the required trigger edge polarities.

- (g) The CHECK/OPERATE/HOLD switch to OPERATE.

- (3) Connect the signal to be totalized to socket 'A' and the electrical timing signals (if used) to socket 'B'.

- (4) Press the Time Base button which will provide suitable units for the count. For example, if the 10<sup>3</sup> switch is depressed the display will be in units of 1000 (within the accuracy of measurement).

- (5) Set the TRIGGER LEVEL controls as required.

- (6) Switching to HOLD stops the automatic clearing of the display. The RESET button should be pressed and released before making a fresh measurement.

- (7) If manual control is required, press the START/STOP button to commence counting and again to terminate counting.

- (8) In order to obtain the true total the displayed reading must be multiplied by the scaling factor 'n' indicated above the selected Time Base push button (see para.2.12 for accuracy).

### BATTERY ECONOMY OPERATION

- 2.14 (1) Prepare the instrument for battery power supply (para.2.1) and normal measurements.

- (2) Set the NORMAL/STANDBY switch to STANDBY and briefly press the RESET button. The instrument will operate for approximately one minute and then revert to standby. To repeat the operation press RESET when instrument is in the STANDBY condition.

### STANDBY OPERATION WITH AC POWER

2.15 The operation described in 2.14(2) can be used with line power. It may be noted that, when switching from NORMAL to STANDBY within one minute of first switching on, the display generally remains on for about one minute before setting into the 'display off' standby condition.

NOTE: The frequency standard oscillator is not switched off in STANDBY and is therefore ready for immediate use.

#### BATTERY CHARGING

- 2.16 (1) Connect the a.c. supply.

- (2) Set the rear panel BATTERY POWER/CHARGE/LINE POWER switch to the CHARGE position.

- (3) Set the front panel Power switch to ON. Verify that the CHARGE indicator is illuminated. The time required for a complete re-charge is 14 hours.

NOTE: The batteries receive a trickle charge when the instrument is operated with rear panel switch in the LINE POWER position.

### **DESCRIPTION OF CONTROLS**

Function Push-Button Switch Bank:

This bank of six press switches, located near the centre of the front panel, select the following measurement modes:-

### (a) T.1.

Provides time interval measurement between two successive events. The events may be on one line (B-B) or separate lines (B-A), with start and stop slopes of the same or opposite polarity.

### (b) T.I. Avg.

This mode is suitable for the measurement of short repetitive events, with start/stop controls as in T.I. By averaging over a number of events the resolution is increased.

### (c) FREQ. A

Provides frequency measurement of the 'A' channel input with readout in kHz.

### (d) PERIOD A

Provides period measurement on 'A' channel signal with readout in microseconds.

(e) RATIO n  $\frac{A}{B}$

Refer to para. 2.10

(f)  $\underline{\text{TOTAL}} \frac{A}{n}$

Provides accumulated total of events applied to Channel 'A', prescaled by a factor 'n' which is selected by use of the Time Base (n) push buttons.

### DESCRIPTION OF CONTROLS (cont'd)

Time Base Range Push- Buttons:

START Slope Switch:

STOP Slope Switch:

Stop Channel Selection Switch:

AC/DC Switch:

This bank of six 'n' switches offers a choice of gate times, and clock units on T.I. The multiplier 'n' associated with each switch may also be defined as follows:-

- (a) The number of periods averaged on 'period average' measurement.

- (b) The 'A' input prescale factor on 'totalize'.

- (c) The 'B' input prescale factor on 'ratio'.

- (d) The number of intervals averaged on 'time interval average'.

A slide switch which selects either positivegoing or negative-going trigger edge for start of time interval and totalize measurements. Applies to Channel 'B' only.

Selects the required 'stop' trigger edge polarity on time interval and totalize on Channel 'A' or 'B', according to the setting of the Stop Channel Selection switch.

Position B selects single line (Channel 'B' only).

Position A selects double line (Start on Channel 'B', Stop on Channel 'A').

This switch selects either a.c. or d.c. coupling in the 'A' channel amplifier.

### Operation on DC Mode

The use of d.c. mode is recommended in the following circumstances:-

- (a) For signals having a slow rate of rise and fall (e.g. sinusoidal signals of frequency lower than 10 Hz).

- (b) For signals of rectangular waveform which have a mark/space ratio other than 1:1, provided the frequency is less than 10MHz.

- (c) Random pulses.

### DESCRIPTION OF CONTROLS (cont'd)

A.C. SENSITIVITY and TRIGGER LEVEL ('A' Channel):

TRIGGER LEVEL Control ('B' Channel)

**HOLD OFF Control**

START/STOP Push Button:

CHECK/OPERATE/HOLD Switch:

This is a dual potentiometer and switch operated by a single control, which performs two functions in the 'A' channel:-

### Sensitivity

The attenuator control is operative on 'A' channel signals when the AC/DC switch is at AC. It is particularly useful in filtering out h.f. interference on lower frequency measurements.

### D.C. Trigger Level

The control provides d.c. offset from -3V to +3V when the AC/DC switch is at DC. If offset is not required the control should be turned fully anti-clockwise to the switched ('0') position.

When the 'A' Channel attenuator is set to X10 the d.c. offset range becomes +30V to -30V.

This control operates in the same manner as the 'A' Channel Trigger Level control described above.

Hold Off is used on Time Interval and Totalize to inhibit the stop input for a period (variable from 0.1ms to 100ms) set by the Hold Off control. This prevents the measured interval being terminated by unwanted signals at the Stop Channel input.

Provides manual start/stop on Time Interval and Totalize modes.

In the OPERATE position the instrument provides continuous updating of the display. In the HOLD position the display is held, but a single shot update can be obtained by depressing the adjacent RESET button.

### DESCRIPTION OF CONTROLS (Cont'd)

In the CHECK position the following facilities are available.

- (a) 1 MHz self check display

- (b) With RESET button depressed an 'all 8's' display is provided for segment check.

- (c) With T.I. function selected the Hold Off delay is displayed.

When the RESET button is depressed and released the instrument will clear down to zero and initiate a new measurement. The RESET button is also used in the segment check and for battery economy operation.

With X1 selected the TRIGGER LEVEL controls have a d.c. offset range of +3v to -3v.

With X10 selected an input attenuator of 20dB is inserted. The d.c. offset range becomes +30V to -30V.

The function of this switch is affected by the setting of the LINE POWER/CHARGE/ BATTERY POWER switch on the rear panel, and by the NORMAL/STANDBY switch.

### POWER ON Position

With LINE POWER selected the a.c. supply is connected to the instrument. Trickle charging of the batteries, if fitted, will take place.

With BATTERY POWER selected the supply from the batteries, if fitted, is connected to the instrument.

With CHARGE selected the batteries, if fitted, will receive a full rate charge derived from the a.c. supply.

#### POWER OFF Position

In the 'off' position, the charging and operating facilities are switched off, irrespective of the type of power supply.

RESET

Push Button:

Attenuator (X1/X10) switches

POWER ON/OFF Switch

### DESCRIPTION OF CONTROLS (Cont'd)

### NORMAL/STANDBY Switch

With NORMAL selected the POWER ON/ OFF switch has its full range of functions. With STANDBY selected:

- (a) With LINE POWER selected only the frequency standard is powered.

- (b) With BATTERY POWER selected the frequency standard is powered and the Battery Economy facility is available.

### **INDICATORS**

OVERFLOW/STANDBY Indicator

BATTERY LOW Indicator:

GATE/CHARGING Indicator:

EXTERNAL STANDARD Indicator:

INPUT TRIGGER Indicators:

MEASUREMENT UNITS

The OVERFLOW indicator will illuminate when the count exceeds the capacity of the 7-digit display or if STANDBY is selected.

Illumination indicates that the batteries will be exhausted within a few minutes.

This indicator illuminates as follows:-

- (a) When the counter gate is 'open'. The illumination period is related to gate time selected.

- (b) When the batteries are receiving full charge a steady illuminaton is obtained (at the same time the readout display will be blank).

This I.e.d. lights when the equipment is in the Frequency or Period mode and an external standard is connected and operating.

These I.e.d.s flash when the input signal is passing through the hysteresis threshold of the associated channel input Schmitt trigger. The indication gives assistance in setting up the d.c. TRIGGER LEVEL control.

The 'ms', 'kHz/ $\mu$ s', 'ns' and 'sec' l.e.d.'s indicate the appropriate unit for the display.

### DESCRIPTION OF CONTROLS (Cont'd)

**HOLD OFF Indicator**

This I.e.d. lights when the HOLD OFF facility is selected.

#### REAR PANEL ITEMS

LINE POWER/CHARGE/BATTERY POWER Switch:

This switch selects the operational power source (battery or line power). The CHARGE position provides full-rate battery charging when the line power is connected and the front panel power switches are at ON and NORMAL.

1 MHz O/P Socket:

A TTL 1 MHz reference signal derived from the frequency standard in use is available at this BNC socket.

Data Output Connector:

The facilities provided by this 28-way connector are listed in Table 1 in the supplement to the Technical Specification.

Marker Output Pins:

The Marker Output Pins allow the user to monitor the state of the Schmitt triggers in the Channel 'A' and 'B' d.c. amplifiers.

Start Inhibit Pin:

A logic '0' on this pin inhibits the Start Channel, allowing unwanted signals to be rejected.

Power Plug:

A three-core power lead is supplied with the instrument.

Power Fuse:

Fuse ratings are annotated on the rear panel . A surge resisting  $5\times20$  mm glass cartridge type must be used.

Osc. Adjust:

This aperture provides access to the calibration adjustment in the frequency standard unit.

Voltage Selection Switch:

This switch has two positions, 'A' and 'B'. It must be set in conjunction with selected tappings on the line power transformer. Instructions for changing voltage range are given in Chap. 5. It is important that the label adjacent to the switch shows the voltage

range selected.

### CHAPTER 3

### PRINCIPLES OF OPERATION

### THE CDI CHIP

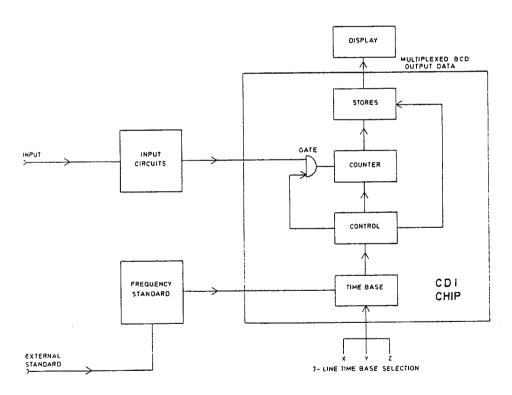

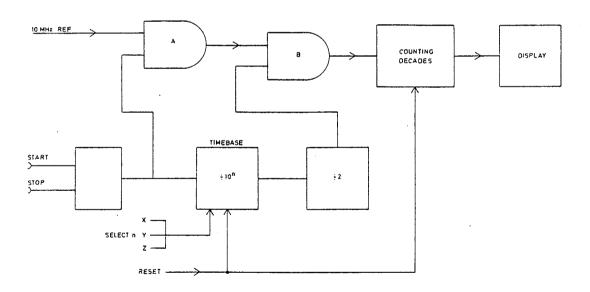

3.1 A basic digital frequency meter comprises a chain of decade counters feeding b.c.d. data into latched stores. Counting is controlled via a main gate which is opened for a period determined by the time base. Provision is made for resetting the counter and releasing the data for display. In the 9904 these functions are carried out in the integrated circuit IC5, which achieves large scale integration, using the collector-diffusion-isolation principle. For convenience, IC5 will often be referred to in the handbook as the 'CDI Chip'.

Basic Frequency Meter

Fig. 3.1

### GENERAL CIRCUIT FUNCTIONS

- 3.2 Outside the CDI Chip, other circuit functions are carried out, such as:-

- (a) Input amplification and signal shaping. Sensitivity control and input (channel) selection.

- (b) A seven-digit display system in bit-parallel byte serial (multiplex) form, with data readout available for external use.

- (c) Clock (reference) frequency generation using a discrete 5MHz oscillator circuit, or a high-stability temperature controlled oscillator. The reference frequency is doubled to 10 MHz for use in the CDI Chip.

- (d) Trigger slope selection, variable trigger hold off, display time control and external reset are provided by means of discrete circuits.

- (e) The power supply system operates from either a.c. line power or optional battery pack using re-chargeable nickel-cadmium cells. Trickle charge and full charge facilities are included. 'Charge' and 'Battery Low' indicators are provided. A 'battery economy' facility is provided.

- (f) Light emitting diode (l.e.d.) indicators are provided as follows:-

- (i) Overflow/Standby:- LP1 lights when the count exceeds the capacity of the seven decade counter. The same indicator lights when the NORMAL/STANDBY switch is set to STANDBY.

- (ii) Battery Low: LP2 indicates the need for re-charging of the batteries. When it lights only a few minutes of battery use is available.

- (iii) Gate/Charging LP3 lights in synchronism with the main gate in the counter, thus showing that measurement is in progress. When the rear panel switch is set to CHARGE the indicator shows that power is available to the charging circuit.

- (iv) External Standard:- LP10 lights when an external frequency standard is connected and operating.

- (v) Trigger Indicators:- LP8 and LP9 light when the input signal passes through the hysteresis threshold of the input Schmitt triggers of the 'A' and 'B' d.c. amplifiers respectively.

- (vi) Measurement Units: LP4 to 7 light to show the appropriate unit for the display.

- (vii) Hold Off: LP11 lights when the Hold Off facility is in use.

### SELF CHECK

3.3 In the Self Check mode the standard frequency of 1 MHz takes the place of the unknown frequency, thus providing a check on the measurement system in the different modes. Facilities for a segment check of the display indicators are also provided.

### AVERAGE PERIOD MEASUREMENT

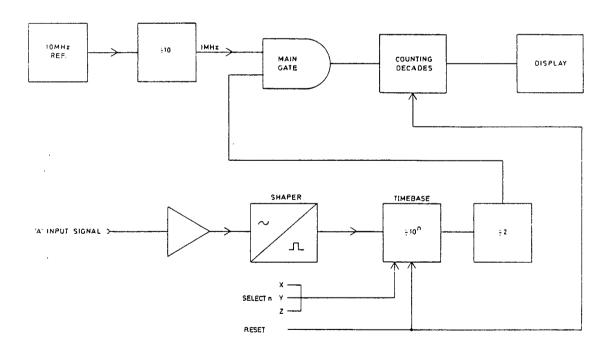

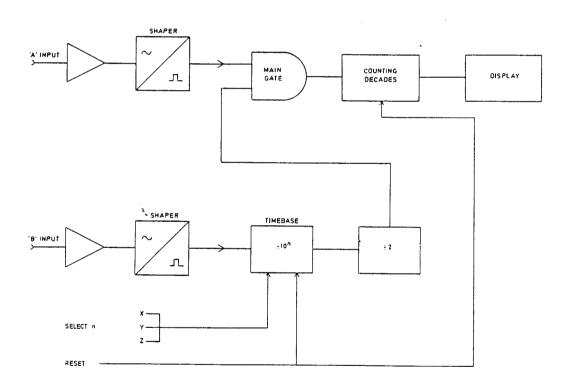

- 3.4 The period of a waveform is measured by counting the number of clock pulses which occur during one or more cycles of that waveform. Greater accuracy is obtained by measuring over as many cycles as possible. As shown in Figure 3.2, the signal of unknown frequency is applied to the 'A' Input and after amplification and shaping is applied to the time base decades. In the time base the unknown signal generates a selection of gate waveforms, one of which is selected by depressing the appropriate time base (n) push-button. The chosen gating waveform is applied to the main gate to control the number of periods during which the measurement is taken.

- 3.5 Clock pulses from the frequency standard are fed to the signal input of the main gate and are counted during the time interval controlled by the selected time base output. The main gate then closes and the display shows the total of clock pulses counted, with decimal point positioned to indicate the average period of the signal.

Period Measurement

Fig. 3.2

### TIME INTERVAL (SINGLE LINE)

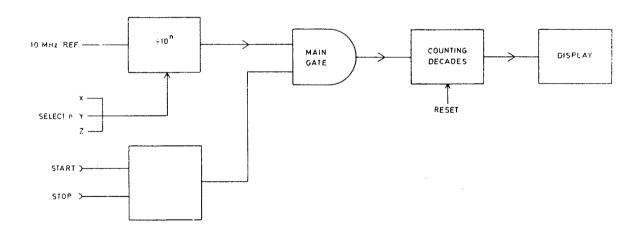

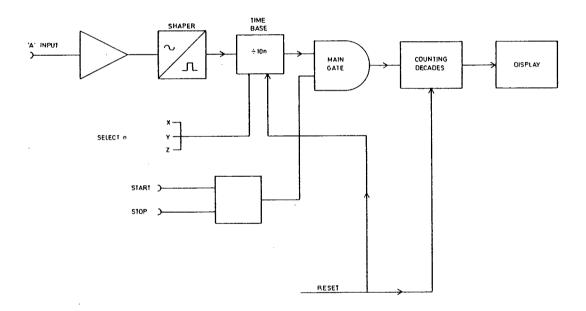

- 3.6 In this mode the instrument is effectively serving as a stop-watch.

Start and Stop signals are supplied from an input on the 'B' channel or by operating the manual START and STOP button. The time interval is measured by counting clock units derived from the frequency standard.

- 3.7 The 0.1 microsecond output from a 10 MHz frequency reference is applied to the time base decades and a suitable clock unit is selected by depressing an appropriate time base push-button. These clock pulses are then coupled to the signal input of the main gate and are totalled in the counter decades during the interval between the Start and Stop signals. At the end of the count the total of time units is displayed. The time value of the chosen unit is indicated by the units indicators.

### TIME INTERVAL (DOUBLE LINE)

3.8 The operating principle is the same as for single line, except that the start and stop signals are on separate inputs. The display will read the true time interval between events on the separate 'A' and 'B' channels.

Time Interval Measurement

Fig. 3.3

### TIME INTERVAL AVERAGE

- 3.9 The reference frequency is 10 MHz. Thus the shortest available clock unit is 100 ns, which places a limit on the resolution available for measurements on, for example, narrow pulse widths. Greater resolution is achieved by the 'averaging' technique, which functions as follows:-

- 3.10 Referring to Figure 3.4 the clock input to the counter has to pass through two gates in series (gates 'A' and 'B' in the diagram). The successive Start and Stop pulses open and close Gate 'A' allowing 10 MHz clock pulses to pass to Gate 'B' during each 'gate open' period. Gate 'B' is held open by the time base for the selected number of intervals and the clock pulses are totalled in the counter. At the end of the selected time base period Gate 'B' closes and the count is displayed as the average time interval.

NOTE: To obtain the improved resolution from time interval averaging, the recurrence frequency of the timing input signal must not be harmonically related to the frequency standard of the counter.

Time Interval Average Measurement

Fig. 3. 4

### **RATIO**

The principle of operation is very similar to frequency measurement, except that the time base output is not derived from the frequency standard. Instead, the lower of the frequencies to be compared is applied to the 'B' Input and divided in the time base. The higher frequency is applied to the 'A' Input and fed via the main gate to the counter. A waveform from the time base decades (derived from the 'B' Input) is selected to gate the 'A' channel signal by depressing an appropriate time base (n) push-button. Since the time base output is a divided version of the 'B' signal, the readout gives a count which corresponds to the ratio of the two input frequencies, multiplied by the factor 'n'. The particular 'n' factor used is that shown adjacent to the selected push-button.

Ratio Measurement

Fig. 3.5

### **TOTALIZE**

- 3.12 The events to be counted are applied to the 'A' Input and, after amplification and shaping, are coupled to the input of the time base decades. An output is selected from an appropriate time base decade by depressing the relevant 'n' push-button. This scaled output is coupled to the signal input of the main gate.

- 3.13 A command level from the START push-button opens the main gate and allows counting to commence; the gate is closed by a command from the STOP push-button. Automatic Start/Stop can be arranged by applying suitable control pulses to the 'B' Input socket.

**Totalizing**

Fig. 3.6

### CONTROL SEQUENCE

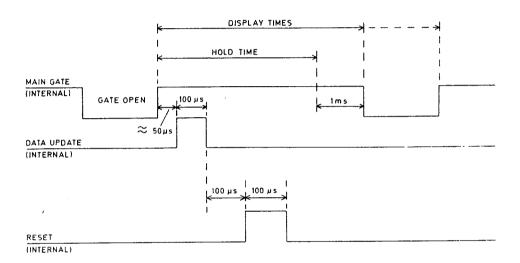

3.14 Figure 3.7 shows the control sequence diagrammatically (not to scale). The longer display time shown in the diagram applies to the latched modes, (Frequency, Period and Ratio).

Control Sequence Diagram

Fig. 3.7

### External Hold

3.15 If, when used with external circuitry, it is required to extend the cycle time, the external hold signal (logic '0') at pin 6 of the data connector, must be applied before the end of the gate or hold time. To allow a new measurement cycle to commence, the external hold input must go 'high' for not less than 200µs.

### External Reset

3.16 For external reset a logic '0' level must be applied to pin 7 of the Data Output connector for a period of not less than 5 ms, 0n reverting to '1' level the display resets to 'all zeros' and a new measurement commences.

### DISPLAY AND DATA OUTPUT SYSTEM

### Multiplex Readout

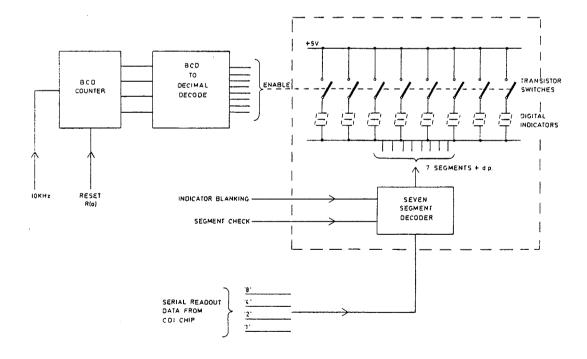

- 3.17 The readout data is fed from the CDI Chip to the display decoder via a four-wire b.c.d. connection. To permit this simple interconnection a parallel-to-serial (multiplex) system is used. The principles are shown in Fig.3.8, although it should be noted that part of the system is in the CDI Chip.

- 3.18 In the CDI Chip the data stores feed in parallel into a common b.c.d. four-line output. The store outputs are enabled in turn for approximately 100 µs by a 10 kHz reference signal, derived from the frequency standard.

- 3.19 The b.c.d. data is fed to a 7-segment decoder (IC25) which offers the decoded data to the bank of I.e.d. digital indicators. The I0 kHz reference signal is fed to a BCD/Decimal decoder which 'enables' each display indicator in turn for 100 µs. A reset pulse R(o) which is generated in the 10° state of the counter, ensures that the display enable is synchronised with the data store readout. A diagram showing the data output format is given on page 12 of the Technical Specification.

Multiplex Display System

Fig. 3.8

3.20 In the display indicators each displayed numeral is formed by illuminating an appropriate number of short straight segments. The numeral '8', for example, is formed from 7 segments, whereas the numeral '4' will require only 4 segments. The segments can be checked by selecting CHECK and pressing the RESET button. This calls up an 'all eights' display.

#### **Decimal Point**

3.21 Decimal point (d.p.) information is obtained by encoding the four line b.c.d. output data from the CDI Chip with the display enable signal. This encode turns on a d.p. drive transistor at the correct instant to light the appropriate decimal point.

#### Control Codes

3.22 A 3-line system is used for time base range selection. The lines are identified as x, y and z, and the logic coding is in Table 3 in the Technical Specification.

### RESISTOR ARRAYS

3.23 Many of the integrated circuits are open collector types. For these IC's discrete 'pull-up' resistors are provided in the circuit. These resistors may be mounted in sealed dual-in-line (d.i.l.) packages, for example R97 (Fig.4) which has thirteen  $1k\Omega$  resistors with a common connection to +5V. Such arrays cannot be serviced and must be changed in the event of a faulty resistor.

### CHAPTER 4

### TECHNICAL DESCRIPTION

### INTRODUCTION

4.1 Apart from some switches and certain items of the power supply, the circuit for the instrument is mounted on one main p.c.b. assembly.

#### LOGIC CIRCUIT SYMBOLS

4.2 Extensive use is made of integrated circuits (IC's) and these are identified by a number and suffix letter. In the circuit description a particular IC pin will be identified by a reference such as 'IC10a/2', which indicates pin 2 on that particular gate. The logic symbols used in the circuits are those found in most manufacturers IC data sheets to which reference should be made if detailed information is required. The CDI Chip IC5 is, however, available only through the Service Department of Racal-Dana Instruments Ltd.

### **OPERATING CONTROLS**

4.3 It is assumed that the reader understands the operational function of each control, as described in Chapter 2.

### FUNCTION AND RANGE SWITCHING

#### Switch Selection

In the circuit diagram, Figure 4 at the back of the book, the Function and Time Base push-button banks S1 and S2 are at the lower left corner. It should be noted that the PERIOD and n(1) switches are shown as selected and all other push-buttons are at 'off'. Switching functions are directed by logic signals, the +5V supply and 'pull-up' resistors being provided in the d.i.l. resistor array R95 and discrete resistors R69, 70, 71 and 72.

#### Control Codes

- 4.5 Operational modes within the CDI Chip are selected by the switch bank \$1 and the a, b and c lines, which are connected via inverters ICld, e and f to IC5. Table 4a gives the logic coding at the switch connections.

- 4.6 Time base selection is made via switch bank S2 and lines x, y and z, which control the gate times in IC5 via the inverters IC1a, b and c. Table 4b gives the logic coding at the switch connections.

TABLE 4a

Function Information

| Function                                 | _ | Cod | e |

|------------------------------------------|---|-----|---|

|                                          | a | b   | С |

| Frequency                                | 1 | 1   | 7 |

| Average Period                           | 0 | 1   | 1 |

| Totalize A                               | 0 | Ì   | 0 |

| Ratio n <u>A</u><br>B                    | 1 | 1   | 0 |

| T.I.(single or double line not averaged) | 0 | 0   | 1 |

| T.I.(single or double line averaged)     | 1 | 0   | 1 |

TABLE 4b

Time Base Selection

| × | <del>-</del> y | Code<br>z | Frequency<br>Gate Time | Multiplier<br>'n' | Time Interval<br>Clock |

|---|----------------|-----------|------------------------|-------------------|------------------------|

| 1 | 1              | 1         | 1 ms                   | 1                 | 0.1 µs                 |

| 0 | 1              | 1         | 10 ms                  | 10 1              | ľμs                    |

| 1 | 0              | 1         | 100 ms                 | 10 <sup>2</sup>   | 10 µs                  |

| 0 | 0              | 1         | 1 sec                  | 10 <sup>3</sup>   | 100 µs                 |

| 1 | 1              | 0         | 10 sec                 | 104               | 1 ms                   |

| 0 | 1              | 0         | 100 sec                | 10 <sup>5</sup>   | 10 ms                  |

### Data Latch/Unlatch

4.7 This is determined by the logic level applied to IC5/4, as follows:-

| Latch    |  |  |  |  |  |  |  |  |  | • | logic | • | '1' |

|----------|--|--|--|--|--|--|--|--|--|---|-------|---|-----|

| Unlatch. |  |  |  |  |  |  |  |  |  |   | logic | : | '0' |

4.8 In Totalize and the two Time Interval modes the data stores in IC5 are unlatched by a logic '0' at IC5/4. This is arranged by Function switch S1 which applies an earth to R70 when the FREQ., PERIOD and RATIO buttons are not selected.

### CHECK/OPERATE/HOLD and Reset

- 4.9 The CHECK/OPERATE/HOLD switch 1S2 is mounted on the Display Assembly and shown on the left hand side of the circuit diagram (Fig. 4). In the OPERATE position the display is continuously updated, the automatic reset being produced within the CDI Chip.

- 4.10 The HOLD connection to the CDI Chip is at IC5/13, the logic requirements at this point are:-

The hold and manual reset signals are applied via the display time generator and associated circuit described in paras. 4,50 to 4.58

4.11 With the CHECK mode selected the 1 MHz standard is applied to the counter circuits to provide an operational check of counter and display in 'Frequency' and 'Period' modes. Pressing the RESET button with CHECK selected gives an 'all 8's' display for segment checking. With CHECK and T.I. selected the Hold Off time is displayed.

#### A CHANNEL INPUT

4.12 The 'A' Channel has alternative amplifier paths, selected by the AC/DC switch 1S1. The two amplifier paths have a common output stage (Q4) which feeds into the counter input of the CDI Chip IC5/22.

### 'A' Channel AC Amplifier

4.13 Signals in the frequency range 10 Hz to 50 MHz which are applied to the 'A' input socket, SK50, are fed via the AC/DC switch (AC position) and capacitor IC1 to the SENSITIVITY potentiometer 1R1a. From 1R1a signals are fed via the C103/R202 combination to the amplifier on the main p.c.b.

- 4.14 The amplifier has a high impedance FET input (Q1) with overload protection provided by R202, D1 and the gate/channel diode. The output from the source of Q1 drives a wideband differential amplifier IC32 which feeds into Q3. Transistor Q2 is turned off in all modes except PERIOD. In PERIOD mode the removal of the earth by switch S1 turns Q2 on, restricting the bandwidth due to the introduction of C9.

- 4.15 Transistor Q3 drives the amplifier IC17c and IC17a. IC17c has feedback applied to give a Schmitt trigger action. The output from IC17a is fed to Q4.

#### DC AMPLIFIERS

4.16 The 'A' Channel DC amplifier and the 'B' Channel amplifier are basically identical.

The description of the 'B' Channel amplifier, trigger level setting, attenuation,

marker output and trigger l.e.d. drive given below applies to both circuits.

### 'B' Channel Amplifier

- 4.17 Input signals at SK51 are fed to the X1/X10 attenuator switch 1S8. This selects either the R12/C5 combination or the R10/R11 attenuator as the path to Q17.

- 4.18 Q17 is a dual FET. One FET is used as an amplifier, the input excursion being limited by D8 and D9. The signal from the source is fed to the inverting input of IC33a, a line receiver having feedback applied to give a Schmitt trigger.

- 4.19 The second FET of Q17 has its gate potential set by the 'B' Channel TRIGGER LEVEL potentiometer, and sets the potential of the non-inverting input of IC33a. This provides control of the trigger level at the input socket over the range ±3V with X1 selected and ±30V with X10 selected.

- 4.20 The signal from IC33a/4 is passed through IC28a, which forms part of the signal selection system described in paragraphs 4.25 to 4.29. The signal at IC28a/3 is passed via IC6a to the Marker Output pin on the rear panel.

- 4.21 The signal from IC28a/3 is also used to control the Trigger lamp drive unit. This circuit provides an indication as to whether the amplifier is being triggered.

Successful triggering of the amplifier is indicated by flashing of the Trigger I.e.d. LP8 at approximately 10 flashes per second.

- 4.22 IC23e and d, R52, R53 and C37 form a multivibrator running at approximately 10Hz. The positive going edge at IC23d/8 is inverted in IC23a, differentiated by C36/R54 and used to preset IC31a. This opens gate IC24a and closes gate IC24b.

- 4.23 In the absence of signal at IC28a/3 (amplifier not being triggered), IC31a remains preset, and the I.e.d. drive is inhibited by IC24b. With signal present, however, the first positive going edge at IC28a/3 will clock IC31a/6 to '1'. The negative going half cycle at IC23d/8, inverted by IC23b, will give a '0' at IC24b/6. The I.e.d. will therefore light for half a cycle of the multivibrator.

4.24 With input frequencies of less than 20Hz IC31a will not necessarily be clocked out of the preset state during the multivibrator half cycle following presetting. The operation of the Trigger I.e.d. would be inhibited even though the 'B' Channel input was in the high state. To prevent this LP8 is lit via IC24a when IC31a is in the preset state and the 'B' Channel input is in the high state.

### SIGNAL SELECTION

- 4.25 The signal at IC5/22 can be obtained from the 'A' Channel AC amplifier, the 'A' Channel DC amplifier or the 1 MHz standard at IC5/6. Selection is made by Q10, Q13, IC28b, IC16e and IC11a. All selected signals are passed through the amplifier Q4.